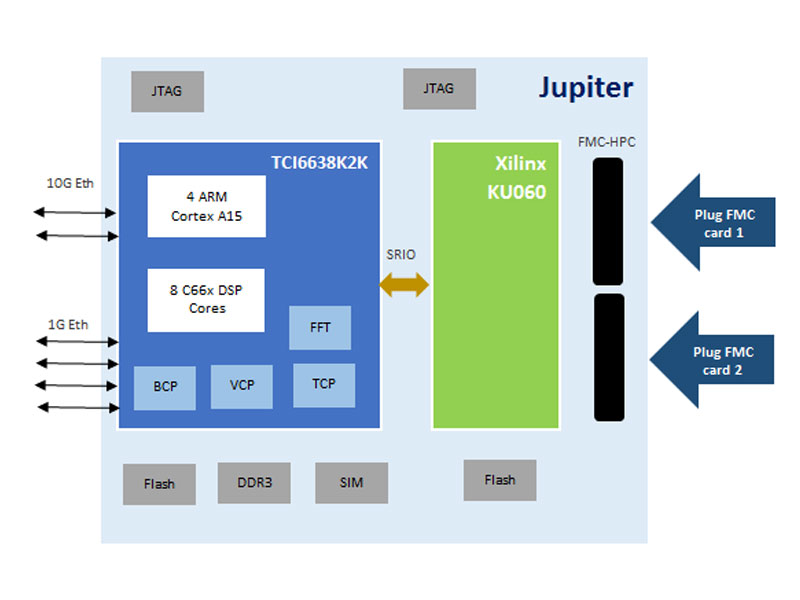

Jupiter is a high-end computing platform for SDR based application. The platform kit provides a jump start for designers of wireless, cable, EW radar or high-performance Radio applications. The platform offers a powerful TI DSP K2K SoC with 8 DSP core and 4 ARM cores along with many HW accelerations suitable for developing communication technologies. The DSP SoC is integrated to a Xilinx UltraScale FPGA over SRIO interface. The Kintex class FPGA has resources to implement front end signal processing algorithms like DDC/DUC/Channel filters/ Crest Factor reduction etc. for multiple antenna systems. The FPGA drives several IO pins for accurate sample level control of elements. The platform offers two industry standard FMC-HPC connectors capable of integrating multiple radio transceiver modules over high speed ADC/DAC interfaces like JESD.

| Interface | Description |

|---|---|

| 4x 1 G Ethernet | 4 RJ 45 Connectors |

| 2x 10 G Ethernet | 2 XFP Connector |

| UART interface to SoC | Through USB connector |

| 2x FMC-HPC connectors | Two FMC connectors for ADC/DAC or radio module integration. |

| DDR3 RAM | 4GB / 8GB RAM |

| Flash | 256MB for Uboot & Kernel / 512MB Storage |